商品簡介

作者簡介

目次

相關商品

商品簡介

本書內容豐富,敘述詳盡清晰,圖文并茂,通過大量的資料和設計實例說明了PCB設計中的一些技巧和方法,以及應該注意的問題,具有工程性好、實用性強的特點。本書共15章,分別介紹了印制電路板(PCB)上焊盤、過孔、疊層、走線、接地、去耦合、電源電路、時鐘電路、模擬電路、高速數字電路、模數混合電路、射頻電路等PCB設計的基礎知識、設計要求、設計方法和設計實例,以及PCB熱設計、PCB的可制造性與可測試性設計、PCB的ESD防護設計等內容。

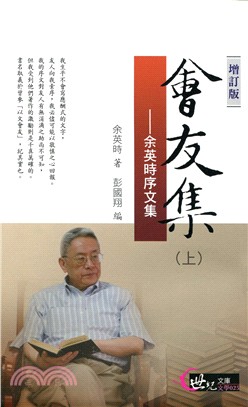

作者簡介

黃智偉(1952.08—),曾擔任衡陽市電子研究所所長、南華大學教授、衡陽市專家委員會委員,獲評南華大學師德標兵,主持和參與完成“計算機無線數據通訊網卡”等科研課題20多項,申請專利8項,擁有軟件著作權2項,發表論文120多篇,出版圖書多部。

目次

第1章 焊盤的設計 1

1.1 元器件在PCB上的安裝形式 1

1.1.1 元器件的單面安裝形式 1

1.1.2 元器件的雙面安裝形式 1

1.1.3 元器件之間的間距 2

1.1.4 元器件的布局形式 4

1.1.5 測試探針觸點/通孔尺寸 8

1.1.6 基準點(Mark) 8

1.2 焊盤設計的一些基本要求 11

1.2.1 焊盤類型 11

1.2.2 焊盤尺寸 12

1.3 通孔插裝元器件的焊盤設計 12

1.3.1 通孔插裝元器件的孔徑 12

1.3.2 焊盤形式與尺寸 13

1.3.3 跨距 13

1.3.4 常用通孔插裝元器件的安裝孔徑和焊盤尺寸 14

1.4 SMT元器件的焊盤設計 15

1.4.1 片式電阻、片式電容、片式電感的焊盤設計 15

1.4.2 金屬電極元器件的焊盤設計 18

1.4.3 SOT 23封裝器件的焊盤設計 19

1.4.4 SOT-5 DCK/SOT-5 DBV(5/6引腳)封裝器件的焊盤設計 20

1.4.5 SOT 89封裝器件的焊盤設計 20

1.4.6 SOD 123封裝器件的焊盤設計 21

1.4.7 SOT 143封裝器件的焊盤設計 21

1.4.8 SOIC封裝器件的焊盤設計 22

1.4.9 SSOIC封裝器件的焊盤設計 23

1.4.10 SOP封裝器件的焊盤設計 23

1.4.11 TSOP封裝器件的焊盤設計 23

1.4.12 CFP封裝器件的焊盤設計 24

1.4.13 SOJ封裝器件的焊盤設計 25

1.4.14 PQFP封裝器件的焊盤設計 25

1.4.15 SQFP封裝器件的焊盤設計 26

1.4.16 CQFP封裝器件的焊盤設計 26

1.4.17 PLCC(方形)封裝器件的焊盤設計 27

1.4.18 QSOP(SBQ)封裝器件的焊盤設計 27

1.4.19 QFG 32/48封裝器件的焊盤設計 28

1.4.20 設計SMT焊盤應注意的一些問題 29

1.5 DIP封裝器件的焊盤設計 31

1.6 BGA封裝器件的焊盤設計 32

1.6.1 BGA封裝簡介 32

1.6.2 BGA表面焊盤的布局和尺寸 33

1.6.3 BGA過孔焊盤的布局和尺寸 35

1.6.4 BGA走線間隙和走線寬度 37

1.6.5 BGA的PCB層數 38

1.6.6 ?BGA封裝的布線方式和過孔 39

1.6.7 Xilinx公司推薦的BGA、CSP和CCGA封裝的PCB焊盤設計規則 39

1.6.8 VFBGA焊盤設計 42

1.6.9 LFBGA 焊盤設計 43

1.7 UCSP封裝器件的焊盤設計 44

1.8 PoP封裝器件的焊盤設計 46

1.8.1 PoP封裝結構形式 46

1.8.2 PoP封裝的層疊和焊盤及布線 47

1.8.3 PoP封裝PCB設計實例 49

1.9 Direct FET封裝器件的焊盤設計 51

第2章 過孔 53

2.1 過孔模型 53

2.1.1 過孔類型 53

2.1.2 過孔電容 54

2.1.3 過孔電感 54

2.1.4 過孔的電流模型 54

2.1.5 典型過孔的R、L、C參數 55

2.1.6 影響過孔特性阻抗的一些因素 56

2.2 過孔焊盤與孔徑的尺寸 57

2.2.1 過孔的尺寸 57

2.2.2 高密度互連盲孔的結構與尺寸 59

2.2.3 高密度互連復合通孔的結構與尺寸 61

2.2.4 高密度互連內核埋孔的結構與尺寸 62

2.3 過孔與焊盤圖形的關系 63

2.3.1 過孔與SMT焊盤圖形的關系 63

2.3.2 過孔到金手指的距離 64

2.4 微過孔 64

2.5 背鉆 65

2.5.1 背鉆技術簡介 65

2.5.2 背鉆設計規則 66

第3章 PCB疊層設計 70

3.1 PCB疊層設計的一般原則 70

3.2 多層板工藝 72

3.2.1 層壓多層板工藝 72

3.2.2 HDI印制板工藝 73

3.2.3 BUM板工藝 75

3.3 多層板的設計 76

3.3.1 4層板的設計 76

3.3.2 6層板的設計 77

3.3.3 8層板的設計 79

3.3.4 10層板的設計 80

3.4 利用PCB疊層設計抑制EMI輻射 82

3.4.1 PCB的輻射源 82

3.4.2 共模EMI的抑制 83

3.4.3 設計多電源層抑制EMI 84

3.4.4 利用拼接電容抑制EMI 84

3.4.5 利用邊緣防護技術抑制EMI 87

3.4.6 利用內層電容抑制EMI 88

3.4.7 PCB疊層設計實例 89

3.5 PCB電源平面和接地平面 91

3.5.1 PCB電源平面和接地平面的功能和設計原則 91

3.5.2 PCB電源平面和接地平面疊層和層序 92

3.5.3 PCB電源平面和接地平面的疊層電容 96

3.5.4 PCB電源平面和接地平面的層耦合 96

3.5.5 PCB電源平面和接地平面的諧振 97

3.5.6 電源平面上的電源島結構 98

3.6 利用EBG結構抑制PCB電源平面和接地平面的SSN噪聲 99

3.6.1 EBG結構簡介 99

3.6.2 EBG結構的電路模型 100

3.6.3 EBG的單元結構 103

3.6.4 基于Sierpinski曲線的分形EBG結構 115

3.6.5 平面級聯型EBG結構 116

3.6.6 選擇性內插式EBG結構 117

3.6.7 多周期平面EBG結構 118

3.6.8 垂直級聯型EBG結構 119

3.6.9 嵌入多層螺旋平面EBG結構 123

3.6.10 接地層開槽隔離型EBG結構 123

3.6.11 狹縫型UC-EBG電源平面 126

3.6.12 嵌入螺旋諧振環結構的電源平面 127

第4章 走線 129

4.1 寄生天線的電磁輻射干擾 129

4.1.1 電磁干擾源的類型 129

4.1.2 天線的輻射特性 129

4.1.3 寄生天線 132

4.2 PCB上走線間的串擾 133

4.2.1 互容 133

4.2.2 互感 134

4.2.3 拐點頻率和互阻抗模型 136

4.2.4 串擾類型 137

4.2.5 減小PCB上串擾的一些措施 138

4.3 PCB傳輸線的拓撲結構 141

4.3.1 PCB傳輸線簡介 141

4.3.2 微帶線 142

4.3.3 埋入式微帶線 143

4.3.4 單帶狀線 143

4.3.5 雙帶狀線或非對稱帶狀線 144

4.3.6 差分微帶線和差分帶狀線 145

4.3.7 傳輸延時與介電常數的關系 145

4.3.8 影響PCB阻抗精度的一些因素 146

4.3.9 微帶線阻抗不連續性的補償方法 148

4.3.10 帶地共面波導效應對微帶線的影響 149

4.3.11 PCB傳輸線設計與制作中應注意的一些問題 150

4.4 低電壓差分信號(LVDS)的布線 155

4.4.1 LVDS布線的一般原則 155

4.4.2 LVDS的PCB走線設計 157

4.4.3 LVDS的PCB過孔設計 160

4.5 PCB布線的一般原則及工藝要求 162

4.5.1 控制走線方向 162

4.5.2 檢查走線的開環和閉環 162

4.5.3 控制走線的長度 163

4.5.4 控制走線分支的長度 163

4.5.5 拐角設計 164

4.5.6 差分對走線 164

4.5.7 控制PCB導線的阻抗和走線終端匹配 168

4.5.8 設計接地保護走線 169

4.5.9 防止走線諧振 169

4.5.10 布線的一些工藝要求 169

第5章 接地 174

5.1 地線的定義 174

5.2 地線阻抗引起的干擾 174

5.2.1 地線的阻抗 174

5.2.2 公共阻抗耦合干擾 180

5.3 地環路引起的干擾 181

5.3.1 地環路干擾 181

5.3.2 產生地環路電流的原因 182

5.4 接地的分類 183

5.4.1 安全接地 183

5.4.2 信號接地 183

5.4.3 電路接地 184

5.4.4 設備接地 186

5.4.5 系統接地 186

5.5 接地的方式 186

5.5.1 單點接地 186

5.5.2 多點接地 188

5.5.3 混合接地 189

5.5.4 懸浮接地 190

5.6 接地系統的設計原則 190

5.6.1 理想的接地要求 191

5.6.2 接地系統設計的一般規則 191

5.7 地線PCB布局的一些技巧 192

5.7.1 參考面 192

5.7.2 避免接地平面開槽 193

5.7.3 接地點的相互距離 195

5.7.4 地線網絡 196

5.7.5 電源線和地線的柵格 197

5.7.6 電源線和地線的指狀布局形式 199

5.7.7 最小化環面積 200

5.7.8 按電路功能分割接地平面 202

5.7.9 局部接地平面 203

5.7.10 參考層的重疊 205

5.7.11 20H原則 206

第6章 去耦合 208

6.1 去耦濾波器電路的結構與特性 208

6.1.1 典型的RC和LC去耦濾波器電路結構 208

6.1.2 去耦濾波器電路的特性 210

6.2 電阻器、電容器、電感器的射頻特性 211

6.2.1 電阻器的射頻特性 211

6.2.2 電容器的射頻特性 212

6.2.3 電感器的射頻特性 213

6.2.4 串聯RLC電路的阻抗特性 214

6.2.5 并聯RLC電路的阻抗特性 214

6.3 去耦電容器的PCB布局設計 215

6.3.1 去耦電容器的安裝位置 215

6.3.2 去耦電容器的并聯和反諧振 221

6.4 使用去耦電容降低IC的電源阻抗 224

6.4.1 電源阻抗的計算模型 224

6.4.2 IC電源阻抗的計算 225

6.4.3 電容器靠近IC放置的允許距離 226

6.5 PDN中的去耦電容器 229

6.5.1 去耦電容器的電流供應模式 229

6.5.2 IC電源的目標阻抗 230

6.5.3 去耦電容器組合的阻抗特性 231

6.5.4 PCB上的目標阻抗 233

6.6 去耦電容器的容量計算 234

6.6.1 計算去耦電容器容量的模型 234

6.6.2 確定目標阻抗 235

6.6.3 確定大容量電容器的容量 235

6.6.4 確定板電容器的容量 236

6.6.5 確定板電容器的安裝位置 237

6.6.6 減小ESLcap 238

6.6.7 mΩ級超低目標阻抗設計 239

6.7 片狀三端子電容器的PCB布局設計 239

6.7.1 片狀三端子電容器的頻率特性 239

6.7.2 使用三端子電容器減小ESL 241

6.7.3 三端子電容器的PCB布局與等效電路 241

6.7.4 三端子電容器的應用 243

6.8 X2Y電容器的PCB布局設計 244

6.8.1 采用X2Y電容器替換穿心式電容器 244

6.8.2 X2Y電容器的封裝形式和尺寸 244

6.8.3 X2Y電容器的應用與PCB布局 245

6.9 鐵氧體磁珠的PCB布局設計 247

6.9.1 鐵氧體磁珠的基本特性 247

6.9.2 片式鐵氧體磁珠 248

6.9.3 鐵氧體磁珠的選擇 250

6.9.4 鐵氧體磁珠在電路中的應用 251

6.9.5 鐵氧體磁珠的安裝位置 252

6.9.6 利用鐵氧體磁珠為FPGA設計電源隔離濾波器 252

6.10 小型電源平面“島”供電技術 259

6.11 掩埋式電容技術 259

6.11.1 掩埋式電容技術簡介 259

6.11.2 使用掩埋式電容技術的PCB布局實例 260

6.12 可藏在PCB7

1.1 元器件在PCB上的安裝形式 1

1.1.1 元器件的單面安裝形式 1

1.1.2 元器件的雙面安裝形式 1

1.1.3 元器件之間的間距 2

1.1.4 元器件的布局形式 4

1.1.5 測試探針觸點/通孔尺寸 8

1.1.6 基準點(Mark) 8

1.2 焊盤設計的一些基本要求 11

1.2.1 焊盤類型 11

1.2.2 焊盤尺寸 12

1.3 通孔插裝元器件的焊盤設計 12

1.3.1 通孔插裝元器件的孔徑 12

1.3.2 焊盤形式與尺寸 13

1.3.3 跨距 13

1.3.4 常用通孔插裝元器件的安裝孔徑和焊盤尺寸 14

1.4 SMT元器件的焊盤設計 15

1.4.1 片式電阻、片式電容、片式電感的焊盤設計 15

1.4.2 金屬電極元器件的焊盤設計 18

1.4.3 SOT 23封裝器件的焊盤設計 19

1.4.4 SOT-5 DCK/SOT-5 DBV(5/6引腳)封裝器件的焊盤設計 20

1.4.5 SOT 89封裝器件的焊盤設計 20

1.4.6 SOD 123封裝器件的焊盤設計 21

1.4.7 SOT 143封裝器件的焊盤設計 21

1.4.8 SOIC封裝器件的焊盤設計 22

1.4.9 SSOIC封裝器件的焊盤設計 23

1.4.10 SOP封裝器件的焊盤設計 23

1.4.11 TSOP封裝器件的焊盤設計 23

1.4.12 CFP封裝器件的焊盤設計 24

1.4.13 SOJ封裝器件的焊盤設計 25

1.4.14 PQFP封裝器件的焊盤設計 25

1.4.15 SQFP封裝器件的焊盤設計 26

1.4.16 CQFP封裝器件的焊盤設計 26

1.4.17 PLCC(方形)封裝器件的焊盤設計 27

1.4.18 QSOP(SBQ)封裝器件的焊盤設計 27

1.4.19 QFG 32/48封裝器件的焊盤設計 28

1.4.20 設計SMT焊盤應注意的一些問題 29

1.5 DIP封裝器件的焊盤設計 31

1.6 BGA封裝器件的焊盤設計 32

1.6.1 BGA封裝簡介 32

1.6.2 BGA表面焊盤的布局和尺寸 33

1.6.3 BGA過孔焊盤的布局和尺寸 35

1.6.4 BGA走線間隙和走線寬度 37

1.6.5 BGA的PCB層數 38

1.6.6 ?BGA封裝的布線方式和過孔 39

1.6.7 Xilinx公司推薦的BGA、CSP和CCGA封裝的PCB焊盤設計規則 39

1.6.8 VFBGA焊盤設計 42

1.6.9 LFBGA 焊盤設計 43

1.7 UCSP封裝器件的焊盤設計 44

1.8 PoP封裝器件的焊盤設計 46

1.8.1 PoP封裝結構形式 46

1.8.2 PoP封裝的層疊和焊盤及布線 47

1.8.3 PoP封裝PCB設計實例 49

1.9 Direct FET封裝器件的焊盤設計 51

第2章 過孔 53

2.1 過孔模型 53

2.1.1 過孔類型 53

2.1.2 過孔電容 54

2.1.3 過孔電感 54

2.1.4 過孔的電流模型 54

2.1.5 典型過孔的R、L、C參數 55

2.1.6 影響過孔特性阻抗的一些因素 56

2.2 過孔焊盤與孔徑的尺寸 57

2.2.1 過孔的尺寸 57

2.2.2 高密度互連盲孔的結構與尺寸 59

2.2.3 高密度互連復合通孔的結構與尺寸 61

2.2.4 高密度互連內核埋孔的結構與尺寸 62

2.3 過孔與焊盤圖形的關系 63

2.3.1 過孔與SMT焊盤圖形的關系 63

2.3.2 過孔到金手指的距離 64

2.4 微過孔 64

2.5 背鉆 65

2.5.1 背鉆技術簡介 65

2.5.2 背鉆設計規則 66

第3章 PCB疊層設計 70

3.1 PCB疊層設計的一般原則 70

3.2 多層板工藝 72

3.2.1 層壓多層板工藝 72

3.2.2 HDI印制板工藝 73

3.2.3 BUM板工藝 75

3.3 多層板的設計 76

3.3.1 4層板的設計 76

3.3.2 6層板的設計 77

3.3.3 8層板的設計 79

3.3.4 10層板的設計 80

3.4 利用PCB疊層設計抑制EMI輻射 82

3.4.1 PCB的輻射源 82

3.4.2 共模EMI的抑制 83

3.4.3 設計多電源層抑制EMI 84

3.4.4 利用拼接電容抑制EMI 84

3.4.5 利用邊緣防護技術抑制EMI 87

3.4.6 利用內層電容抑制EMI 88

3.4.7 PCB疊層設計實例 89

3.5 PCB電源平面和接地平面 91

3.5.1 PCB電源平面和接地平面的功能和設計原則 91

3.5.2 PCB電源平面和接地平面疊層和層序 92

3.5.3 PCB電源平面和接地平面的疊層電容 96

3.5.4 PCB電源平面和接地平面的層耦合 96

3.5.5 PCB電源平面和接地平面的諧振 97

3.5.6 電源平面上的電源島結構 98

3.6 利用EBG結構抑制PCB電源平面和接地平面的SSN噪聲 99

3.6.1 EBG結構簡介 99

3.6.2 EBG結構的電路模型 100

3.6.3 EBG的單元結構 103

3.6.4 基于Sierpinski曲線的分形EBG結構 115

3.6.5 平面級聯型EBG結構 116

3.6.6 選擇性內插式EBG結構 117

3.6.7 多周期平面EBG結構 118

3.6.8 垂直級聯型EBG結構 119

3.6.9 嵌入多層螺旋平面EBG結構 123

3.6.10 接地層開槽隔離型EBG結構 123

3.6.11 狹縫型UC-EBG電源平面 126

3.6.12 嵌入螺旋諧振環結構的電源平面 127

第4章 走線 129

4.1 寄生天線的電磁輻射干擾 129

4.1.1 電磁干擾源的類型 129

4.1.2 天線的輻射特性 129

4.1.3 寄生天線 132

4.2 PCB上走線間的串擾 133

4.2.1 互容 133

4.2.2 互感 134

4.2.3 拐點頻率和互阻抗模型 136

4.2.4 串擾類型 137

4.2.5 減小PCB上串擾的一些措施 138

4.3 PCB傳輸線的拓撲結構 141

4.3.1 PCB傳輸線簡介 141

4.3.2 微帶線 142

4.3.3 埋入式微帶線 143

4.3.4 單帶狀線 143

4.3.5 雙帶狀線或非對稱帶狀線 144

4.3.6 差分微帶線和差分帶狀線 145

4.3.7 傳輸延時與介電常數的關系 145

4.3.8 影響PCB阻抗精度的一些因素 146

4.3.9 微帶線阻抗不連續性的補償方法 148

4.3.10 帶地共面波導效應對微帶線的影響 149

4.3.11 PCB傳輸線設計與制作中應注意的一些問題 150

4.4 低電壓差分信號(LVDS)的布線 155

4.4.1 LVDS布線的一般原則 155

4.4.2 LVDS的PCB走線設計 157

4.4.3 LVDS的PCB過孔設計 160

4.5 PCB布線的一般原則及工藝要求 162

4.5.1 控制走線方向 162

4.5.2 檢查走線的開環和閉環 162

4.5.3 控制走線的長度 163

4.5.4 控制走線分支的長度 163

4.5.5 拐角設計 164

4.5.6 差分對走線 164

4.5.7 控制PCB導線的阻抗和走線終端匹配 168

4.5.8 設計接地保護走線 169

4.5.9 防止走線諧振 169

4.5.10 布線的一些工藝要求 169

第5章 接地 174

5.1 地線的定義 174

5.2 地線阻抗引起的干擾 174

5.2.1 地線的阻抗 174

5.2.2 公共阻抗耦合干擾 180

5.3 地環路引起的干擾 181

5.3.1 地環路干擾 181

5.3.2 產生地環路電流的原因 182

5.4 接地的分類 183

5.4.1 安全接地 183

5.4.2 信號接地 183

5.4.3 電路接地 184

5.4.4 設備接地 186

5.4.5 系統接地 186

5.5 接地的方式 186

5.5.1 單點接地 186

5.5.2 多點接地 188

5.5.3 混合接地 189

5.5.4 懸浮接地 190

5.6 接地系統的設計原則 190

5.6.1 理想的接地要求 191

5.6.2 接地系統設計的一般規則 191

5.7 地線PCB布局的一些技巧 192

5.7.1 參考面 192

5.7.2 避免接地平面開槽 193

5.7.3 接地點的相互距離 195

5.7.4 地線網絡 196

5.7.5 電源線和地線的柵格 197

5.7.6 電源線和地線的指狀布局形式 199

5.7.7 最小化環面積 200

5.7.8 按電路功能分割接地平面 202

5.7.9 局部接地平面 203

5.7.10 參考層的重疊 205

5.7.11 20H原則 206

第6章 去耦合 208

6.1 去耦濾波器電路的結構與特性 208

6.1.1 典型的RC和LC去耦濾波器電路結構 208

6.1.2 去耦濾波器電路的特性 210

6.2 電阻器、電容器、電感器的射頻特性 211

6.2.1 電阻器的射頻特性 211

6.2.2 電容器的射頻特性 212

6.2.3 電感器的射頻特性 213

6.2.4 串聯RLC電路的阻抗特性 214

6.2.5 并聯RLC電路的阻抗特性 214

6.3 去耦電容器的PCB布局設計 215

6.3.1 去耦電容器的安裝位置 215

6.3.2 去耦電容器的并聯和反諧振 221

6.4 使用去耦電容降低IC的電源阻抗 224

6.4.1 電源阻抗的計算模型 224

6.4.2 IC電源阻抗的計算 225

6.4.3 電容器靠近IC放置的允許距離 226

6.5 PDN中的去耦電容器 229

6.5.1 去耦電容器的電流供應模式 229

6.5.2 IC電源的目標阻抗 230

6.5.3 去耦電容器組合的阻抗特性 231

6.5.4 PCB上的目標阻抗 233

6.6 去耦電容器的容量計算 234

6.6.1 計算去耦電容器容量的模型 234

6.6.2 確定目標阻抗 235

6.6.3 確定大容量電容器的容量 235

6.6.4 確定板電容器的容量 236

6.6.5 確定板電容器的安裝位置 237

6.6.6 減小ESLcap 238

6.6.7 mΩ級超低目標阻抗設計 239

6.7 片狀三端子電容器的PCB布局設計 239

6.7.1 片狀三端子電容器的頻率特性 239

6.7.2 使用三端子電容器減小ESL 241

6.7.3 三端子電容器的PCB布局與等效電路 241

6.7.4 三端子電容器的應用 243

6.8 X2Y電容器的PCB布局設計 244

6.8.1 采用X2Y電容器替換穿心式電容器 244

6.8.2 X2Y電容器的封裝形式和尺寸 244

6.8.3 X2Y電容器的應用與PCB布局 245

6.9 鐵氧體磁珠的PCB布局設計 247

6.9.1 鐵氧體磁珠的基本特性 247

6.9.2 片式鐵氧體磁珠 248

6.9.3 鐵氧體磁珠的選擇 250

6.9.4 鐵氧體磁珠在電路中的應用 251

6.9.5 鐵氧體磁珠的安裝位置 252

6.9.6 利用鐵氧體磁珠為FPGA設計電源隔離濾波器 252

6.10 小型電源平面“島”供電技術 259

6.11 掩埋式電容技術 259

6.11.1 掩埋式電容技術簡介 259

6.11.2 使用掩埋式電容技術的PCB布局實例 260

6.12 可藏在PCB7

主題書展

更多

相關商品

主題書展

更多書展今日66折

您曾經瀏覽過的商品

購物須知

大陸出版品因裝訂品質及貨運條件與台灣出版品落差甚大,除封面破損、內頁脫落等較嚴重的狀態,其餘商品將正常出貨。

特別提醒:部分書籍附贈之內容(如音頻mp3或影片dvd等)已無實體光碟提供,需以QR CODE 連結至當地網站註冊“並通過驗證程序”,方可下載使用。

無現貨庫存之簡體書,將向海外調貨:

海外有庫存之書籍,等候約45個工作天;

海外無庫存之書籍,平均作業時間約60個工作天,然不保證確定可調到貨,尚請見諒。

為了保護您的權益,「三民網路書店」提供會員七日商品鑑賞期(收到商品為起始日)。

若要辦理退貨,請在商品鑑賞期內寄回,且商品必須是全新狀態與完整包裝(商品、附件、發票、隨貨贈品等)否則恕不接受退貨。